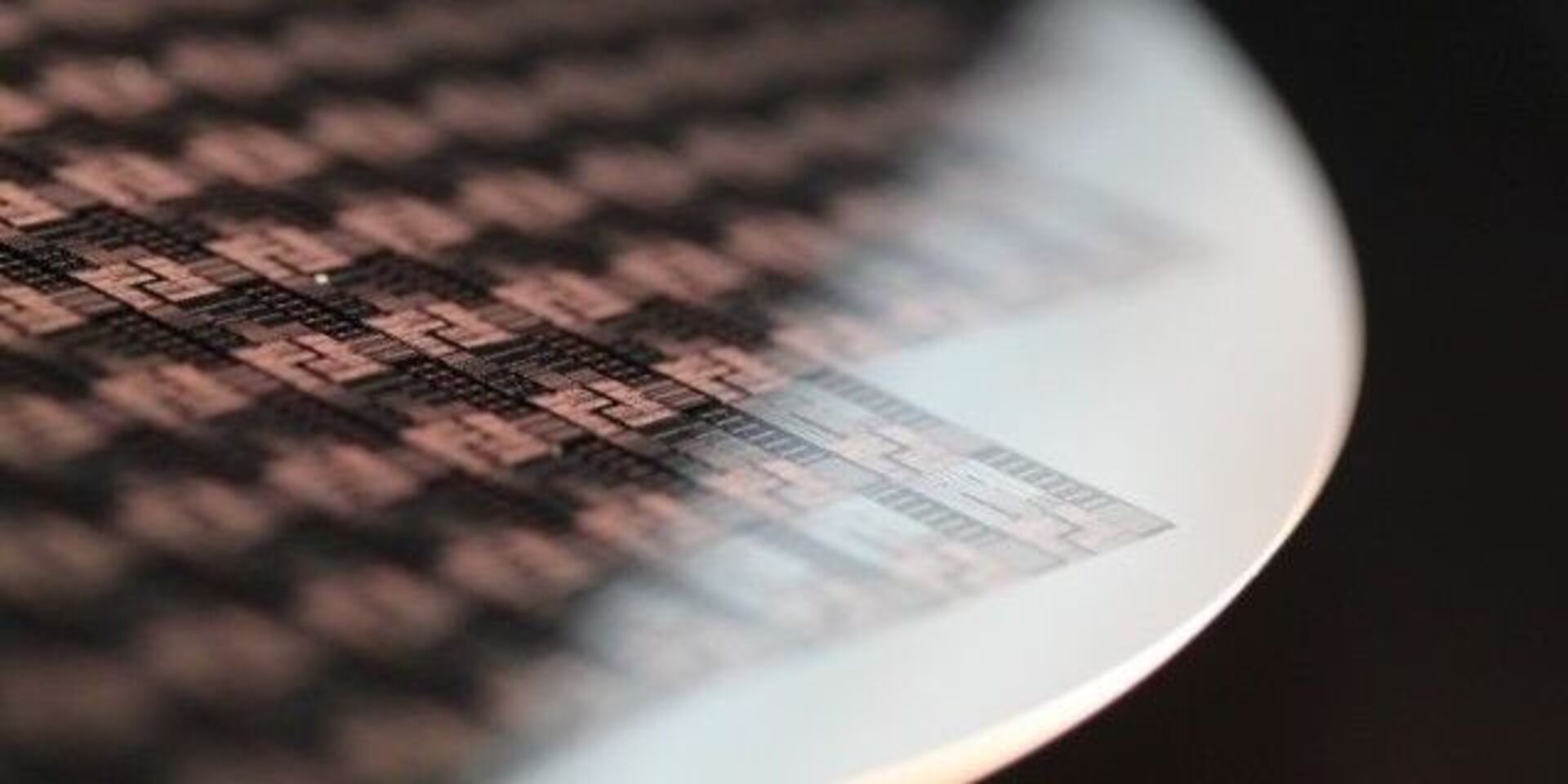

Quelle: Fraunhofer Institut

Marco Plüss/Fraunhofer Institut

Was ein Waferaustausch ermöglicht

Das Fraunhofer IPMS und CEA-Leti haben den ersten Austausch von ferroelektrischen Speicherwafern innerhalb der FAMES-Pilotlinie erfolgreich abgeschlossen. Damit wurde ein wichtiger Meilenstein bei der gemeinsamen europäischen Plattform für fortschrittliche eingebettete nichtflüchtige Speichertechnologien erreicht. Mit diesem Erfolg hat die im Dezember 2023 gestartete und von CEA-Leti koordinierte Pilotlinie unter Beweis gestellt, dass komplexe Waferprozesse zwischen zwei führenden Forschungsinstituten in Europa ausgetauscht und gemeinsam bearbeitet werden können.

Die Zusammenarbeit konzentriert sich auf die Herstellung und elektrische Charakterisierung von ferroelektrischen Kondensatorstapeln aus Hafnium-Zirkoniumoxid (HZO). Unter Nutzung der kombinierten 300-mm-CMOS-Reinraumkapazitäten beider Institute wurden die Wafer in kurzen Prozessschleifen ausgetauscht, um eine gemeinsame Bewertung von Materialien, Elektrodenkonfigurationen und Bauelementverhalten zu ermöglichen. Bei der erfolgreichen Bearbeitung an zwei Standorten wurden auch die in der Pilotlinie implementierten Protokolle für den Waferaustausch und die Kontaminationskontrolle validiert und gezeigt, dass auch komplexe Materialstapel in verschiedenen Reinräumen auf allen Wafern zuverlässig verarbeitet werden können.

Nahtloser Wafer-Austausch zwischen den FAMES-Standorten

"Dieser erste Austausch zwischen CEA-Leti und dem Fraunhofer IPMS zeigt, dass gemeinsame Prozessabläufe, Testvehikel und Charakterisierungsumgebungen nahtlos zwischen den FAMES-Standorten funktionieren können", erklärt Projektkoordinator Dominique Noguet. "Die Einrichtung zuverlässiger Wafer-Loops zwischen führenden Forschungsinstituten ist für die Beschleunigung der Entwicklung ferroelektrischer Speicher unerlässlich."

Mit Blick auf die Zukunft legen die Wafer-Loops den Grundstein für eine breitere Zusammenarbeit in der Entwicklung. In den nächsten Phasen werden HfO?-basierte ferroelektrische Stapel von Fraunhofer IPMS in CEA-Leti-CMOS-Prozesse integriert, gefolgt von Bewertungen auf Array-Ebene von neuen Speichertechnologien. Die Roadmap umfasst auch Studien zu Elektrodenprozessvariationen, Langzeitzuverlässigkeit und Back-End-of-Line-Integrationsansätzen.

Parallel dazu hat das Fraunhofer IPMS kürzlich einen ersten Chip-Tape-out mit der 22-nm-FDX®-Technologie von GlobalFoundries abgeschlossen und mit der Forschung an algorithmischen KI-Compute-in-Memory-Beschleunigerarchitekturen begonnen, die auf diesen ferroelektrischen Technologien aufbauen.